Collaborative Cache, Inc. owns the patent for a revolutionary computer architecture that has an invention date of October 5, 2022.

Background:

Since the time of uniprocessors, multitasking has enabled multiple tasks to execute concurrently creating the appearance of running simultaneously. The processor cache was a transparent fast copy of memory. In 1965 when multiprocessors were introduced, the cache remained transparent.

The Claim:

The Independent-Cache Collaboration protocol states that when every processor maintains the integrity of its own cache and memory, then no processor needs to be concerned with other caches. The caches are independent. They do not need hardware coherence.

The multitasking software knows what data needs to be shared with other processors, but does not have the ability to communicate that information to the hardware. Data needs to be shared with other processors if and only if the same data is shared with other tasks. The result of this principle is that data that is not shared with other tasks does not require hardware coherence.

Systems programmers write reentrant code to protect the memory integrity of the program from other tasks. Reentrant programs have data that can not be modified by other tasks. Program logic protects that data from the other tasks. This same protection will protect the memory integrity of the program data from other processors. The software already minimizes shared memory access because holding a lock causes resource contention. The software logic already distinguishes shared data.

Coherence is a hardware problem that has no hardware solution. Because the software has additional information, the software already has the solution. Currently software has no way to convey the coherence information to the hardware. But when the architecture is modified, coherence vanishes, poof.

Currently swapping a task to another processor creates a need for hardware coherence. This could be addressed by supplying a CPU ID to the coherence controller. However adopting a Collaborative OS eliminates swapping, eliminates multitasking, and even eliminates locks. All that is possible because the architecture has unlimited scalability.

The Architecture:

The new architecture runs any existing multitasking operating system that uses an HSP. The new architecture enables replacing existing multitasking operating systems with a Collaborative Operating System that permits simultaneous execution. Instead of tasks that appear to execute concurrently but actually multitask, tasks will be delegated to other processors and execute simultaneously. This requires many processors, so coherence has heretofore prevented development in this direction.

The new architecture runs existing multitasking operating systems while permiting multitasking to be replaced. Processor affinity permits the architecture to multitask more efficiently.

The Benefit:

Eliminating coherence enables scalable processors that each run single threaded tasks to completion. Tasks that now run concurrently on multiple processors with locks using shared memory tables will instead run single threaded without locks using cache resident tables.

Take a step back - everything changes when the cache is a fast exclusive memory instead of a fast transparent copy of memory.

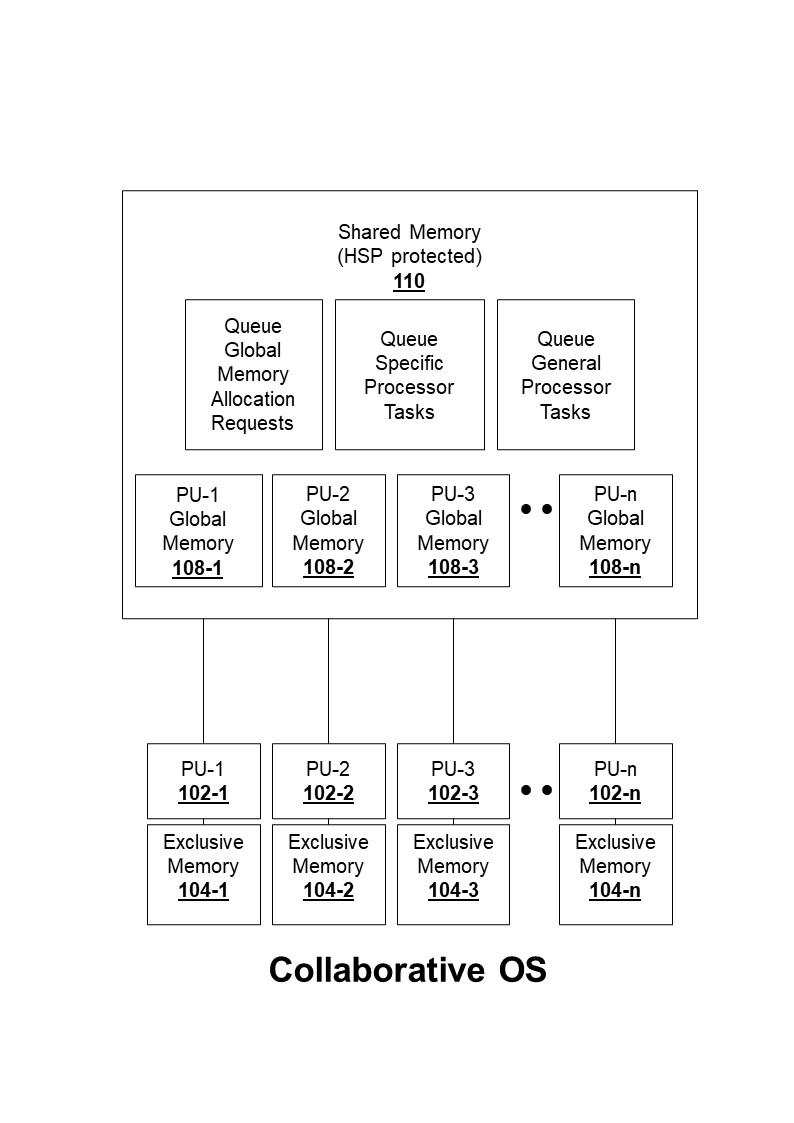

The diagram below depicts HSP protected Shared Memory as consisting of Global Memory and queues. Exclusive Memory is protected because it is not altered by other tasks. The result is no Coherence required!

No coherence permits unlimited processors permits single threading which permits exclusive tables and eliminates locks.

Background:

Since the time of uniprocessors, multitasking has enabled multiple tasks to execute concurrently creating the appearance of running simultaneously. The processor cache was a transparent fast copy of memory. In 1965 when multiprocessors were introduced, the cache remained transparent.

The Claim:

The Independent-Cache Collaboration protocol states that when every processor maintains the integrity of its own cache and memory, then no processor needs to be concerned with other caches. The caches are independent. They do not need hardware coherence.

The multitasking software knows what data needs to be shared with other processors, but does not have the ability to communicate that information to the hardware. Data needs to be shared with other processors if and only if the same data is shared with other tasks. The result of this principle is that data that is not shared with other tasks does not require hardware coherence.

Systems programmers write reentrant code to protect the memory integrity of the program from other tasks. Reentrant programs have data that can not be modified by other tasks. Program logic protects that data from the other tasks. This same protection will protect the memory integrity of the program data from other processors. The software already minimizes shared memory access because holding a lock causes resource contention. The software logic already distinguishes shared data.

Coherence is a hardware problem that has no hardware solution. Because the software has additional information, the software already has the solution. Currently software has no way to convey the coherence information to the hardware. But when the architecture is modified, coherence vanishes, poof.

Currently swapping a task to another processor creates a need for hardware coherence. This could be addressed by supplying a CPU ID to the coherence controller. However adopting a Collaborative OS eliminates swapping, eliminates multitasking, and even eliminates locks. All that is possible because the architecture has unlimited scalability.

The Architecture:

The new architecture runs any existing multitasking operating system that uses an HSP. The new architecture enables replacing existing multitasking operating systems with a Collaborative Operating System that permits simultaneous execution. Instead of tasks that appear to execute concurrently but actually multitask, tasks will be delegated to other processors and execute simultaneously. This requires many processors, so coherence has heretofore prevented development in this direction.

The new architecture runs existing multitasking operating systems while permiting multitasking to be replaced. Processor affinity permits the architecture to multitask more efficiently.

The Benefit:

Eliminating coherence enables scalable processors that each run single threaded tasks to completion. Tasks that now run concurrently on multiple processors with locks using shared memory tables will instead run single threaded without locks using cache resident tables.

Take a step back - everything changes when the cache is a fast exclusive memory instead of a fast transparent copy of memory.

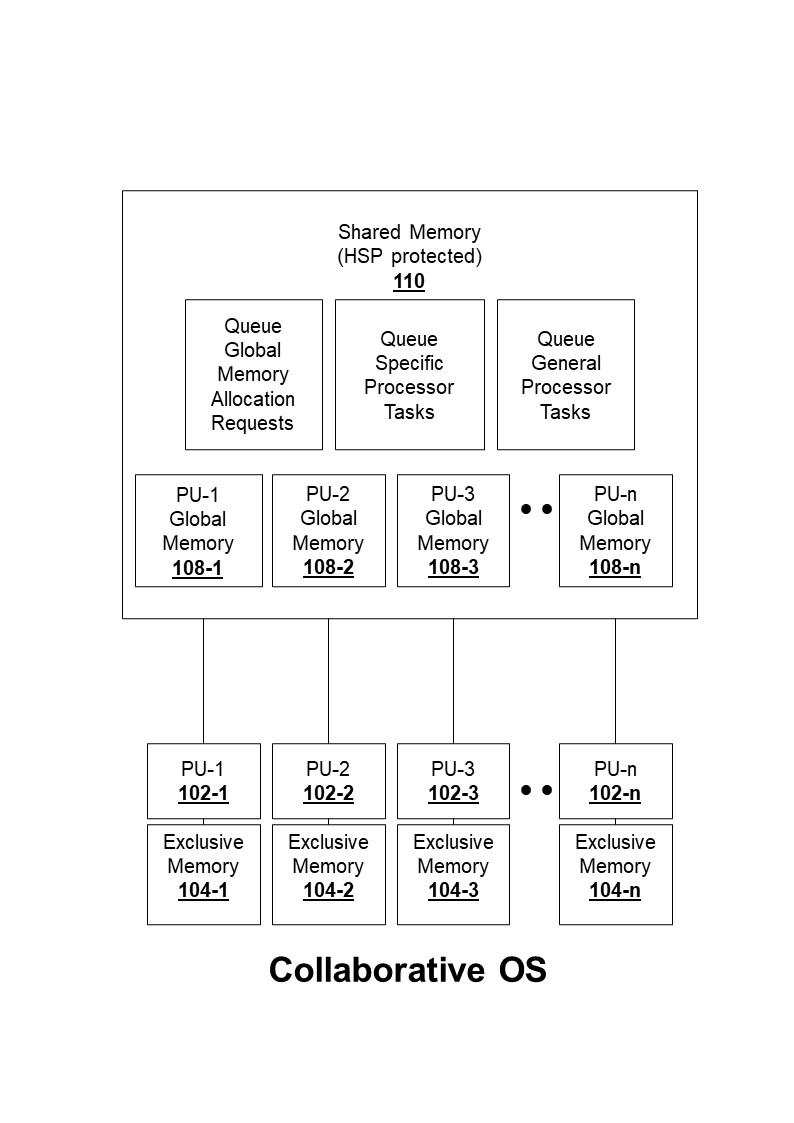

The diagram below depicts HSP protected Shared Memory as consisting of Global Memory and queues. Exclusive Memory is protected because it is not altered by other tasks. The result is no Coherence required!

No coherence permits unlimited processors permits single threading which permits exclusive tables and eliminates locks.

This is not an offering which can only be made by prospectus.

For more information:

Chip Manufacturers contact License@CollaborativeCache.com

OS Developers contact Specs@CollaborativeCache.com

For News Releases contact Press@CollaborativeCache.com

Venture Capital contact Invest@CollaborativeCache.com